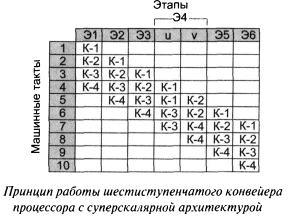

Процесорът, построен върху суперскаларна архитектура, има две (или повече) на конвейера, за да изпълнява команди. Това дава възможност да се извърши едновременно два (или повече) отбора. За да се разбере по-добре полезността на суперскаларна процесорна архитектура, нека да разгледаме предишния пример на конвейер, в който сме приели за простота, че командата стъпка (S4) трае само за един цикъл на машината. А какво ще стане, ако стъпка за извършване S4 екип отнема 2 машинни цикъла? След това се появи прекъсване на транспортиращите, както е показано на фигурата.

Процесорът не е в състояние да отидете на фазата на изпълнение на Е4 Екип К2, докато тя е напълно завършена K1 отбор фаза на изпълнение. В резултат на команда цикъл изпълнение К-2 увеличение от един цикъл на машината, т.е. докато чака за освобождаването на конвейера в стъпка S4. До степен, че на конвейерни допълнителни команди, някои от неговите етапи ще бъде празен ход (на фигурата, те са в сиво).

За борба престой използва neskoleo konveyyerov. Процесорът Intel Pentium се прилага 2 тръбопроводите. Той е първото семейство процесори IA-32, построен върху суперскаларна архитектура. The Pro процесор Pentium първи път е приложен към конвейера 3.

Продължаваме внимание на този пример конвейер шест скорост и въвеждане Eshe он (т.е. втората) конвейера него. Както и преди, ние приемаме, че фазата на изпълнение на екип E4 отнема 2 машинни цикли. Както е показано на фигурата, на нечетните командата пристига в U-конвейер, и командата за четен брой - за V-образен ремък. Този подход позволява да се премахнат престой в операцията на конвейера.

Меморандумът за разбирателство с архитектура използва изпълнението на паралелно извършване на команди за множество конвейери, с решение за паралелно изпълнение на командите е получил процесор хардуера по време на изпълнение. Ефективно използване на такива машини изисква специална оптимизация машинен код в компилатор за генериране на двойки от независими команди (когато в резултат на една команда аргумент не е друг).

Суперскаларна MP може да издаде за изпълнение на всеки цикъл на променлив брой команди и експлоатация на техните транспортьори могат да бъдат планирани или статично чрез компилатор, и с помощта на динамична оптимизация на хардуер. Суперскаларна машини използват инструкция ниво паралелизъм чрез изпращане на няколко команди на нормалния поток инструкция на няколко функционални единици.

В типичен апарат суперскаларна машина може да изпълнява издаване на 1 до 8 команди в един цикъл. Обикновено тези екипи трябва да бъдат независими и да отговарят на определени ограничения, например, така че във всеки цикъл не може да бъде издадена на повече от една команда достъп до паметта. Ако някой отбор в потока на инструкцията е логично зависим или не отговаря на критериите за екстрадиция за изпълнение ще се издава само на екипа преди това. Затова и команда издаване на скоростта суперскаларна машини е променлива

ArhitekturyCisc

RISC архитектура

MCS-51 (Intel 8051) - класически микроконтролер архитектура. За нея има кръстосано асемблер ASM51, освободен Metalink Corporation.

В допълнение, много компании - разработчици на софтуер, като IAR и Кайл, представиха своите възможности за сглобяване. В някои случаи използването на асемблер е по-ефективно, благодарение на удобен набор от директиви и наличието на среда за програмиране, която съчетава професионалния асемблер и C език за програмиране, за корекция на грешки и ръководител на софтуерни проекти.

Понастоящем има два Atmel производство компилатор (AVRStudio 3 и AVRStudio4). Вторият вариант - не се опитвайте да коригирате много успешно първия.

Като част от проекта на AVR-ССЗ (известен още като WINAVR) има компилатор AVR-като (той вече е пренесен към AVR асемблер GNU като izGCC).

Има и свободни минималистични компилатор Avra [1].

Свързани статии