Умножение в двоичен умножение се извършва както в десетичната система. Както си спомняте от училище, разбира се, най-лесният за изпълнение умножение в колона. При прилагането на този алгоритъм, ще трябва да се размножават всеки бит в съответния бит на множителя множителя.

Помислете като например chetyrohrazryadnyh умножение на две двоични числа с. Да предположим, че искате да умножите броя 10112 (1110), на броя на 11 012 (1310). Като резултат от умножението, очакваме да получите номер 100011112 (14310). Извършване на размножаване в колона в двоичната система, както е показано на фигура 15.10.

Фигура 15.10 - Операция на размножаване в колона

За образуване на продукта е необходимо да се изчисли четирите частични продукти. Моля, имайте предвид, че е необходимо в двоична аритметика за извършване на умножение само цифрите от 0 и 1. Това означава, че трябва да се обобщи множимо на сумата от останалите частичните произведения, или не. В резултат на това за формиране на частичен продукт можете да използвате логически елементи "2i", свързани помежду двоично на множителя.

За да се образуват частично продукт, с изключение на умножение от един бит, е необходимо да се извърши смяна на ляво от броя битове, съответстващи на коефициента на теглото на изхвърлянето. Промяната може да бъде осъществено чрез проста връзка на съответните части от частични продукти до необходимата разряд двоичен ехидна.

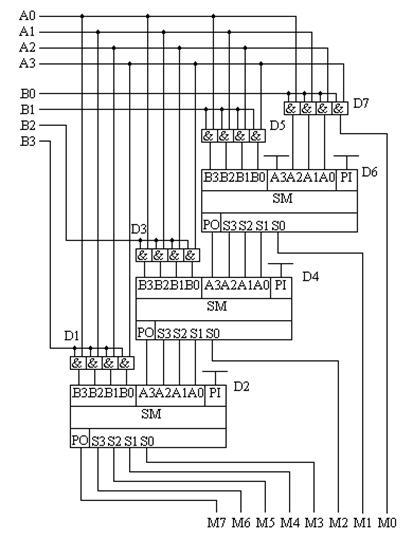

Към схематична диаграма на множителя е подобен на двоичен алгоритъм размножаване, е показан на фигура 14.10 ние използваме условно графични чипове, където входовете са разположени отгоре и отдолу обекти. Той е ограничен до гости. В пълно съответствие с алгоритъма за умножение в колона имаме нужда от три chetyrohrazryadnyh усойница.

Схема на множителя прилага двоичен алгоритъм умножение в колона е дадена на фигура 15.11.

Образуването на частични продукти в схемата, показана на фигура 15.11, да цифрова схема D1, D3, D5 и D7. Тези чипове, които се съдържат в един пакет само четири логически елемент "2i".

Ехидна конфигуриран D6 чип, добавя първата и втората частична продукт. Така LSB първите частни строителни работи, не се нуждае от сумиране (вж. Фигура 15.11). Поради това се подава директно към изхода на множител (ниво M0).

Втората самостоятелна работа трябва да бъде изместен от една цифра. Това се постига с това, че LSB изхода на D6 на суматор е свързан към втория освобождаване продукт (М1). Но след това е необходимо първата частна работа, за да се движат една цифра вляво по отношение на втория конкретния продукт!

Фигура 15.11 - Понятието матрица множител 4'4

Това аритметична операция се извършва така, че LSB вход група А е свързан с първата частна разряд продукт, първите входове от отговорност групи, свързани към втора разрядни частни дела и т.н. Въпреки това, MSB вход група А не се свързва с нищо!

За да се разреши това противоречие не забравяйте, че ако пишем отляво на числото нула, стойността на първоначалния брой няма да се промени, така че ние имаме този бит е свързан с общата схема тел, като по този начин добавянето на нула в най-важния бит от първите частни строителни работи.

По същия начин сумиране се извършва в резултат на трети и четвърти самостоятелен продукт. Тази операция се извършва чип D4 и D2 съответно. За разлика от строителството на схемата е само в това, че не е необходимо да се мисли за най-ниската цифра на предишната сума, защото предишното ехидна чип генерира носене сигнал за последващото чип.

Търсите най-тясно мултипликатор верига показан на фигура 14.11 ние можем да видим, че тя образува матрицата, образувана от веригите, които носят цифри от А и Б. Броят на точките на пресичане на тези схеми са логически елементи "2i". Именно поради тази причина, мултипликатори, изпълнявани в рамките на тази схема са известни като матрица множители.

Скоростта на веригата, показана на фигура 14.11, максималното време за размножаване се определя от най-дългия път на сигнала. Това е пътят, който преминава през чип D7, D6, D4, D2. операция верига време може да се намали, ако не и разширители подредени последователно, като се приема, алгоритъма на фигура 14.10, и обобщение на частичните продукти по двойки, след това се сумират двойки частични продукти и т.н. В този случай времето за умножение е значително намален.

Особено забележимо подобрение на производителността при изграждането на многобитови множители. Въпреки това, нищо не е безплатно. В замяна на увеличаването на скоростта ще трябва да плати до увеличаване на малко ехидна, и по този начин сложността на веригата. Ако Adders частни строителни работи, ще останат със същата дължина дума, както и преди, малко разширители двойки частични продукти следва да бъдат увеличени по един.

Бит разширители четворни частични продукти е два бита вече малко ехидна на частични продукти, тъй като сумиране на четири броя на стойността в най-неблагоприятния случай може да се увеличи четирикратно, и т.н.

Цифрови матрични множители са широко използвани в схеми за обработка на сигнали за промяна на устройството за предавателно отношение, за осъществяване на честотни преобразуватели, и като компонент на цифрови филтри.

А сега да разгледаме следния блок, не по-малко често използваните схеми в цифрова форма и обработка на сигнали. Това памети само за четене.

Свързани статии