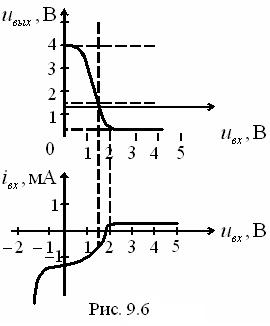

Фиг. 9.6 показва взаимосвързаната вход и трансфер характеристика. Графиките показват, че преди да достигне нивото на прага на входното напрежение до 1.5 V транзистор VTN наситен и вход характеристика е почти линейна. Когато отрицателно напрежение се прилага към етапа на въвеждане има рязко увеличение на абсолютната стойност на входен ток, което води в крайна сметка до повреда. В реални устройства за защита, свързани между излъчвателя и на земята включва ограничаване на диоди.

характеристики изход - е връзката между входния ток входното напрежение. Помислете за тази верига за двете логически състояния на изхода. Фиг. 9.7 показва еквивалентна схема на типична характеристика изход и отворите логика елемент, т.е. елемент, когато сигналът на изхода 0. Текущ 16 mA за максимално допустимите спецификации.

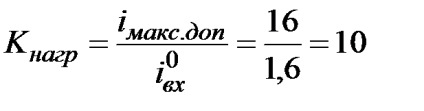

Заредете фактор определя броя на входните елементи, които могат да бъдат едновременно свързани към изхода на един елемент. Известно е, че в различни състояния на логика елемент вход ток с различна стойност :. а. Ето защо:

Максималният брой на входа е 8 TTL елементи.

Динамичните характеристики отразяват преходни процеси при смяна на състояния на логически елементи. Те включват скоростта, продължителността, пускане и спиране на елементи, както и имунитет.

Продължителността на включване и изключване на елементите се определят от следните изрази:

.

Тук и - съответно дължината и изключване ръбове и и - съответно закъснение сигнал, докато преминаването на елемента на 0 и 1. Наличието на продължителността на процеса на превключване, причинени от презареждане на паразитни капацитети и инерцията на транзисторите. Тези параметри са показани в ris.9.9 както добре.

Изпълнение се характеризира със средно време на забавяне:

.

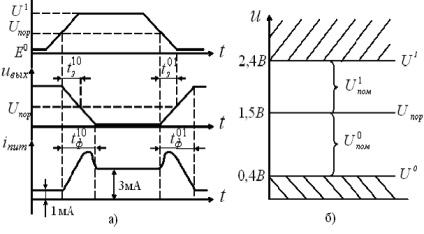

Шум имунитет се характеризира с параметрите е показана на Фиг. 4.9 б.

Изпълнения TTL схеми с допълнителен

В реални устройства често се използва обновен елемент TTL схема с подобрени характеристики и допълнителни функции. Фиг. 9.10, а намалената версия на схемата на инвертора с подобрени характеристики на натоварване.

Логически елементи за изход може да бъде в три състояния: 1, 0 и Z (импеданс или изключено състояние). Ние въвеждат допълнителни елементи във веригата, така че базовата логика клетка има състояние Z. Надстроен схема е показана на Фиг. 4.14, б. Тук, прекъсната линия, посочена от нови елементи. Ако входния файл е елемент 1. изпълнява 2И-НЕ функционира. Ако входът е основателно, на колектора ток на транзистора VTN е нула, всички транзистори са затворени, на изхода на нула.

Свързани статии