RS тригер на И портата - НЕ. Таблицата с истината, режими на работа.

Trigger. Основни понятия на RS тригер, или - не. Таблицата с истина. операция.

Exclusive OR, XOR - НЕ. истина маса. Графично представяне на елементите.

Схема NOR включва ИЛИ порта и инвертор и осигурява отрицание резултат ИЛИ верига.

И врати - НЕ, ИЛИ - НЕ. истина маса. Графично представяне на елементите. графици за работа.

НЕ Шофиране (инвертор) изпълнява отрицание.

Когато най-малко един вход схема ИЛИ е единица на изхода ще бъде единица.

Осъществява съединение или дизюнкцията на две или повече логически стойности.

Единицата на изходната верига и след това ще само ако всички входове са едно. Когато най-малко един вход е нула, на изхода също ще бъде нула.

Логически порти AND, OR, че не. Истината маси, схематични диаграми.

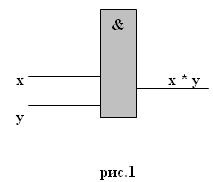

Символ на структурните схеми и схеми с два входа е показано на фигура 1 и таблица истина в таблица 1.

Фиг. 4.1. Наименованията за елементи на изключително или: външна (вляво) и руски (в дясно)

Съгласно XOR функция имаме предвид следното: изхода на единица се случва, когато само един входен блок е налице. Ако входните звена на две или повече, или ако всички входове са нули, а след това на изхода ще бъде нула. Истината маса два входа изключителна ИЛИ елемент е показан в таблица. 4.1. Символи, използвани в местни и чуждестранни схеми са показани на фиг. 4.1. Надписът на национално определяне на изключителна или "= 1" просто означава, че ситуацията се освобождава, когато входът е една и само една единица.

XOR елементи в стандартната серия малко. Вътрешен серия оферта LP5 чипове (четири две вход елемент с 2С освобождаване), LL3 и LP12, които се различават от LP5 на освобождаване ОК. Твърде специфична функция се изпълнява от тези елементи.

В математически термини, елементът XOR извършва т.нар модул 4. Поради това, тези елементи също са посочени като пепелянки модул две. Както вече бе споменато в предишната глава, означен по модул 2 плюс знак, затворена в кръг.

Основното приложение на изключителни или елементи, още от следващата истина таблицата е сравнение на две входни сигнали. В случая, когато входовете на двата блока идват до нула или две (същите сигнали), нулева се генерира на изхода (вж. Таблица 4.1.). Обикновено в такава прилагане на постоянно ниво, се подава към един вход елемент, който се сравнява с променливи във времето сигнал пристигането на другия вход. Но по-често на специален код чип за сравнение се използват за сравнение на сигналите и кодове, които ще бъдат обсъдени в следващата глава.

Както разширител по модул 2 елемент XOR използва в успоредни и последователни модул две разделители, които служат за изчисляване циклична контролна сума. Но детайлите на тези схеми ще бъдат разглеждани в лекциите 14.15.

Важен прилагане на изключителни или - се контролира от инвертор (фигура 4.2.). В този случай един от входния елемент се използва като контрола и друга информация, вход елемент сигнал се подава. Ако контрол входен блок, входният сигнал е обърнат, ако нула - не обърнати. В повечето случаи, управляващ сигнал се дава постоянно ниво, определящ елемент на работа, както и на информационния сигнал е импулс. Това означава, че ексклузивно елемент може да се променя поляритета на входа или сигнал, или не може да се променя в зависимост от управляващия сигнал.

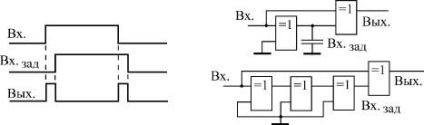

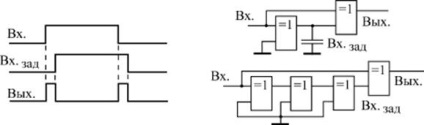

Фиг. 4.2. Element XOR като контролирано инвертор

В случая, когато има два сигнала на една и съща полярност (положително или отрицателно), и по този начин едновременно пристигането им изключени XOR елемент може да се използва за смесване на тези сигнали (фиг. 4.3). С или полярността на сигнали изходните сигнали ще бъде положителен елемент. За положителни сигнали на изключителни или елемент ще действат като елемент 2 или, както и с отрицателен ще замени 2I-НЕ елемент. Такива замествания могат да бъдат полезни в случаите, когато в схемата остават неизползвани някои елементи XOR. Вярно е, че ние трябва да помним, че закъснението на разпространението на сигнала в ексклузивно ИЛИ обикновено е малко по-висока (около 1.5 пъти), отколкото забавянето при най-простите елементи и, NAND, OR, NOR.

Фиг. 4.3. Прилагане на изключителни или елемент за смесване на две не-едновременно сигнали

Фиг. 4.4. Изолиране на фронтовете на входния сигнал чрез изключителна ИЛИ елемент

Друго важно приложение на изключителна ИЛИ елемент - (. Фигура 4.4) образуване на кратки импулси съгласно всяка ръба на входния сигнал. В този случай, не е важно, положителния вход или отрицателно ръб, изходът още положителен импулс се генерира. Входният сигнал се забави с кондензатор или верижни елементи, а след това на оригиналния сигнал и забавено копието се подава към входа на елемент ИЗКЛЮЧВАЩО ИЛИ. В двете схеми като елементите за закъснение се използват като елементи на два входа изключителна ИЛИ неинвертиращ включен (в неизползван вход е нула). Като резултат от тази трансформация можем да говорим за удвояване на честотата на входния сигнал, тъй като изходящите импулси следват два пъти по-често, колкото на входа.

Тази функция елементи XOR трябва да се разглежда в случаите, когато са налице различни сигнали едновременно двата входа на елемента. В изходен елемент може да доведе до фалшиви кратки импулси, съгласно всяка една от фронтовете на входните сигнали. Премахване на тяхното влияние върху по-нататъшното веригата може, например, чрез синхронизиране, подобна на тази, разгледана в предишния раздел.

RS-тригер - спусъка е отделен набор от логически състояния на нула и единица (с отделен двигател). Той има два входа за данни S и Р. На влизане S тригер е настроен на Q = L (/ Q = 0) и от влизане R - в състояние Q = О (/ Q = 1).

Асинхронни RS-задействания. Те са най-простите спусъците. Като независим устройство използва рядко, но са добра основа за по-сложни тригери. В зависимост от логическата структура разграничи RS-тригери с преки и обратни входове. Техните схеми и символи могат да бъдат намерени на фиг. 2.37. Тригерите от този тип са изградени на два логически елементи: 2 NOR - спусък с директни входове (. Фигура 2.37, а), 2 NAND - флоп с обърната вход (Фигура 2.37, Ь.). Изходът на всеки от елементите на логически е свързан с един от входовете на друг елемент, който осигурява спусъка две стабилни състояния.

Фиг. 2.37. Асинхронни RS-тригери: а - RS-тригер на врата, и NOR и символ; Б - RS-тригер на врата, и NOR и символ.

състояние Trigger под влиянието на конкретна комбинация от входни сигнали е показано в таблицата за работа (щати) (Таблица. 2.18).

Таблица 2.18. Статус на спусъка.

В Qn (/ Qn) таблици определени нива, които са били на изходите на праговите да предоставят на нейните входове така наречените активни нива. Активният разговор логично ниво действащи на входа на NAND порта и еднозначно идентифицира логично изходното ниво (независимо от нивото на логически, работещи на други входове). За ИЛИ-НЕ елементи като активно ниво на високо ниво на - 1 и на И-НЕ - ниско ниво - нива О. които се хранят един от входовете не се променя нивото на логиката на изхода на елемент, наречен пасивен. Нива Qn + 1 (/ Qn + 1) означават логически нива на изходите тригер след информацията в нейните входове. За да се задейства директно входа през доставка на входа сигнал съзвездие S = 1, R = 0, до получаване на изхода Qn + 1 = 1 (/ Qn + 1 = 0). Такъв режим се нарича логически запис единица.

Ако отстранява от S единица сигнал, т. Е. комплект към входния S на нула сигнал, статус спусъка не се променя. S режим = 0, R = 0 се нарича режим на съхранение на информация, тъй като информацията на изхода остава непроменена.

При прилагането на сигнал S входния = 0, R = 1, тригер ще премине и изхода ще Qt + 1 = 0 (/ Qn + 1 = 1). Такъв режим се нарича режим на запис логика нула (режим на нулиране). Когато S = R = 1, състоянието на тригер ще бъде сигурно, поради ефекта на информационен сигнал логически нива на изходите тригер са идентични (Qn + 1 = / Qn + 1 = 0) и след техните действия задействат еднакво да може да приеме една от две стабилни състояния. Следователно, такава комбинация на S = R = 1 е забранено.

За да се затвори с обърнати входове на режима запис единица логиката се реализира с / S = 0 R = 1, логиката нула режим / запис - с / S = 1, / R = 0. В / S = / R = 1, осигуряват съхранение на информация. Комбинация Input / S = / R = 0 е забранено.

RS тригер се нарича с името на техните входове. Вход S (Определете -. Engl набор) позволява Q изхода на тригера на едно състояние. Вход R (Reset -. Изчисти Engl) позволява да се изчисти изходния тригер Q (Quit -. Добив Eng) до нула.

За осъществяване на RS тригер употреба логически елементи "2и-НЕ". Неговата схематична диаграма е показана на фигура 2.

Фигура 2. Схема на прост РС задейства по схеми "2и-НЕ". R и S входове обърнати (активен uroven'0)

Разглеждане на операцията е показано на Фигура 2 RS тригер схема по-подробно. Да предположим, че R и S са входен блок потенциали. Ако изхода на горната част на NAND порта "NAND 2I" Q има логическа нула, на изхода на долната NAND порта "NAND 2I" се появява логическа единица. Това устройство потвърждава логиката нула на изхода Q. Когато "2и-НЕ" се появява на изхода на горната част на NAND порта "NAND 2I" Q първоначално присъства логически блок, на изхода на долната NAND порта логическа нула. Това ще потвърди логично една нула на изхода Р. Това е, когато отделните нива на въвеждане, RS тригер верига работи по същия начин, както на схема на инвертора.

Ще се осигури вход S на нула потенциал. Според таблицата на истината на NAND порта "NAND" на изхода Q ще бъде капацитетът на единица. Това ще доведе до появата на обратен изхода на потенциал спусъка нула. Сега, дори и да се премахне нула потенциал към входа S, устройството ще остане възможност да задейства изхода. Тоест, ние сме записани в блока на спусъка логика.

По същия начин, можем да запишем тригер и логическа нула. За да направите това, трябва да използвате вход R. Тъй като активното ниво на входа е нулева, а след това тези входове - обърнати. Събиране таблица на RS тригер истина. R и S входове в тази таблица ще бъдат използвани директно, че е нула и за запис, и модула за запис ще се извършват от единични потенциали (Таблица 1).

Таблица 1. Таблица на RS тригер истина.

RS тригер могат да бъдат конструирани на логическите елементи "или". спусъка на РС построен на логически елементи "ИЛИ" е показан на Фигура 3. Единствената разлика в работата на тази схема в сравнение с предходната RS тригер верига се състои във факта, че изпълнението и инсталирането на спусъка ще бъде един логически нива. Тези функции са свързани с принципите на обърната логика, която досега се смятаха.

Фигура 3. Схема на прости RS тригер в схемите "ИЛИ". R и S входове пряка (активна "1" ниво)

Тъй като RS тригер когато изграждане на логически елементи "И" и "ИЛИ" работи по същия начин, е условно графично представяне на диаграми веригата е също същото. Свързани графично изображение на RS тригер електрически схеми, дадени на фигура 4.

Фигура 4. Условно графична нотация RS тригер

Пример: Активиране на спусъка положителен ръб и съживяването на отрицателен спусъка. Синхронни RS задействат.

Свързани статии