Схема ускорено транспорт - логическа компютър възел представлява мулти-малко аритметика единица, състояща се от множествена аритметика битови възли при генериране на трансфер на сигнали за по-малко време, отколкото в едноцифрени суматорите.

принцип на работа

[Условия:

Предварителен преглед ръчен единица (LCU) - схема на ускорено транспорт

Извършва Look-напред Adder (CLA) - суматор верига ускорено трансфер

PG - група пренасяне на сигнала размножаване

поколение пренасяне на сигнала група - GG

При използване на предварителен преглед пренос единица (LCU) всеки унарна цифра на суматора произвежда поколение на предаване на сигнала (g0) и предаването на разпространение на сигнала (p0).

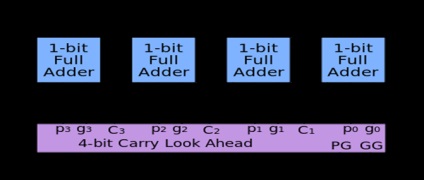

4-битова схема

4-битов разширител със схемата на ускорена транспорт

разширител едно ниво са обединени в групи от по четири единична освобождаване във всяка група. предварителен преглед пренос единица генерира трансфер на сигнали С1, С2, С3, С4, поколение трансфер група сигнал (GG) и сигнал за трансфер група размножаване (PG).

За да прехвърлите един единствен-малко:

За преводи в четири цифри:

Заместването на инч след това. След това, за да получите удължаване на уравнението:

4-битов предварителен преглед пренос единица се произвежда в интегрирана форма: SN74182 (TTL), MC10179 (ECL) и MC14582, 564IP4 [1] (CMOS).

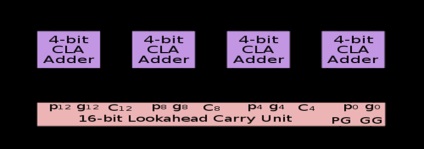

16-битов верига

16-битов разширител може да бъде създаден чрез комбиниране на четири 4-битови суматорите с четири предварителен преглед пренос единица (4-битов CLA Adder), допълнена пета схема на ускорено транспорт, който се използва за обработка на генериране на сигнал група прехвърляне - GG и да размножаване - PG.

Приети входните сигнали трансфер разпространяват () и всеки от четирите генерирани сигнали вериги (). След това, единицата за предварителен преглед пренос генерира съответните сигнали.

Да приемем, че този сигнал и тази на аз-ти. изходните битове са определени, както следва:

Замествайки в първата. след това. тогава се получи след разширяването на израза:

Освен това е възможно да се изчисли пренос размножаване сигнали и генерира верига трансфер за прехвърляне на ускорено:

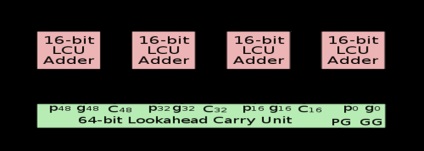

16-битов усойница със схемата на ускореното транспорт

Комбинирането на четири от суматор схема и схема на ускорено транспорт заедно получи 16-битов разширител на. Четири такива блокове могат да се комбинират в 64-битов усойница. По-бързо верига трансфер (второ ниво), необходими за получаване на разпространението на трансфер на сигнали () и генериране на сигнали за трансфер () на всеки разширител на веригата.

64-битов ехидна верига с второ ниво на ускорена транспорт

Предимства и недостатъци

Предимства: висока скорост.

Недостатъци: Висока цена на оборудването

формиращи схеми паралелни трансферни имат значително предимство в скоростта серийни вериги преди трансфера.

Относно: Vstanovlennya аз nalashtuvannya parametrіv робот HDD, diskovodіv че privodіv optichnih nosіїv.

Мета: Nabutov vmіn аз navikіv в vstanovlennі че nalashtuvannі parametrіv робот HDD, diskovodіv че privodіv optichnih nosіїv.

Свързани статии