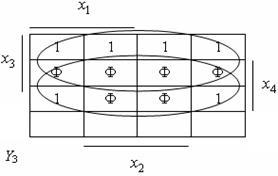

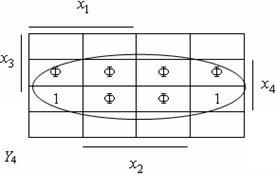

Фиг. 4.1. Карти на Карно код конвертор

Веригата се прави въз основа на тези основа структурна формула И-НЕ, е показана на Фиг. 4.2.

Фиг. 4.2. Блоковата схема на кодовете на предавателя

Шифрованата - конвертори позиционен код в двоично, т.е. трансдукция на сигнала 1 в един от входовете на съответния код на изходните автобуси ... Ако изходът се отстранява m - битов код, максималният брой входове п = 2 m. Ако всички 2 м входове, като енкодер се нарича пълна, ако не всички - на непълен. Работа на енкодер 4 февруари представена истина маса (табл. 4.2). се вижда от таблицата:

т. е. за изграждане на енкодера изисква две LE или два входа.

Енкодери са конструирани подобно на по-голям брой битове.

Недостатъкът на тези енкодери - неяснотата, ако образувано няколко входа. Отговори за енкодер само един развълнуван вход изграждане приоритет енкодер. В тях, в случай на едновременно възбуждане на множество входове, кодът продукция ще съответства на "голям" ( "по-млади") развълнуван брой входове. Фиг. 4.3 показва определянето на енкодера. Приоритет енкодер има допълнителни изводи: E1 - даде възможност на сигнала енкодер, E0 - сигнал за липса на развълнуван вход, на G - изходния сигнал, което показва наличието на най-малко един от най-развълнуван вход.

Наличието на заключения Е1. E0, G позволява да се увеличи енкодери битови.

Decoder - n- битов конвертор двоичен код в единна 2 п-битовия код, т.е., на декодера има п входове и m = 2 п изходи ... Всеки набор от входни променливи, отговарящи на възбуждане (външния вид на логически един или нула) на изхода, десетично число, което съответства на двоичен код.

Вземем примера на строителството на две-битов декодер. Функционирането на декодера може да бъде представен чрез таблица истина От масата се получи израз за изход функции (Y1) декодер (таблица 4.3.):

От тези отношения е ясно, че изграждането на декодера изисква четири и порти в два входа и два инвертори. декодери са изградени често в база И-НЕ (вж. фиг. 4.4). В този случай резултатите са обърнати, т.е. развълнуван продукция съответства на логическа нула ..; и да получи директен достъп, е необходимо да се четири инвертор. За да се разширят функциите на декодер в интегрални схеми и друг вход E - разрешение. За неговата организация идват от И-не на 3 входа - третите входове заедно и образуват резолюцията вход. В този случай, дешифриращия работи, когато входният E логическа единица.

Фиг. 4.4. Структурата на декодера

Графично представяне на декодери показани на Фиг. 4.5. Ако резултатите са обърнати, определеният кръгове.

Наличието на активирате вход позволява да се увеличи декодер малко. Фиг. 4.6 показва как да се изгради трицифрен декодер, използвайки двуцифрен.

Фиг. 4.6. декодери Капацитет

За всички набори от входни променливи, където x3 = 0, DC ще работят 2, т. За. На входа E2 единица ще дойде. Когато x3 = 1, съответно работещ декодер DC 3. По този начин, има три входа и осем изхода. За да увеличите броя на входовете и изходите, можете да използвате паралелен (правоъгълна) декодер, но и за това, с изключение на декодерите, необходими елементи 2i.

Използването на декодери и допълнителни порти логика може да реализира почти всяка функция логика.

Да разгледаме следния пример

Таблицата с истината за тази функция е на масата за форма. 4.4. Неговото прилагане изисква декодера 2 Април и схемата ИЛИ до два входа (фиг. 4.7). Когато Х1 и Х2 са равни на единство (да се създаде п = 1 и п = 2), се появява единица и съответно изхода функция ще бъде равно на 1 при изходите на декодера (1 или 2).

Фиг. 4.7. Структурно ехидна верига

модул 2 декодер

Работа на две-битов мултиплексор представя истината маса (табл. 4.5). Работа мултиплексор описано логично уравнение

В съответствие с уравнението за изграждане на мултиплексор нуждае 3I-4 или елемент и два инвертори. Структурна схема е показана на Фиг. 4.8, графично представяне на мултиплексори - на фиг. 4.9.

Фиг. 4.7. Структурна схема мултиплексор

Фиг. 4.9 Символ мултиплексори

Фиг. 4.10. мултиплексори капацитет Схема

Фиг. 4.12. Имитация на картина

демултиплексорна

Трябва да се отбележи, че мултиплексори и демултиплексори в серия използват биполярни транзистори пътуват само цифрови сигнали, т.е.. Е. 0 или 1.

Фиг. 4.12. Функционална схема на мултиплексор-демултиплексиращото

Той нарича комбинаторни ехидна верига за добавяне на двоични числа. Най-простият проблем - добавянето на две едноцифрени числа. За да се развие логика, трябва първо да разгледа всички възможни комбинации на входните променливи, въз основа на които можете да създадете таблица на щата. Следните комбинации могат да се наблюдават при добавяне на едно-битови числа А и В:

т. е. ако А = В = 1, за прехвърляне към следващата (по-значително) бит. Следователно, като ехидна трябва да има два изхода: един за формиране на част от сумата, свързана с тази категория, а вторият - да се прехвърлят към следващата цифра. Представяне на числа и логически променливи a0. b0. образува състояние масата, където S0 (Таблица 4.8.) - сума, Р - да сигнал.

Следователно това представлява логично уравнение PDNF:

и изграждане на блоковите диаграми (фиг. 4.14, Фиг. 4.15).

Фиг. 4.14. Adder модул две Фиг. 4.15. схема за трансфер

Веригата прилага уравнение 1 се нарича XOR се разрежда серийно като единичен чип. Графично представяне е даден на фигура 4.16. Логическата операция, извършена от тази верига, -

където - сумиране по модул символ две.

Свързани статии