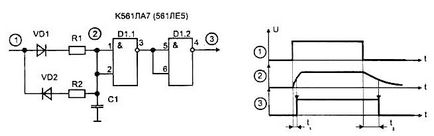

Понякога е необходимо да се премине от водещите и прилежащите краища на правоъгълен импулс. Най-простият схема на реализация на такъв проблем е показано на фиг. 1.58. С появата на фронта на вълната кондензатор С1 започва да се зарежда въвеждане чрез верига VD1-R1, и с появата на криза - изпуска през VD2-R2. Това ви позволява да избирате отделни забавяне превключване LE. Максималното време за забавяне на пулса на предния и упадъка не може да надвишава 80% от дължината на входния сигнал.

Фиг. 1.58. Време пулс забавяне на RC-вериги

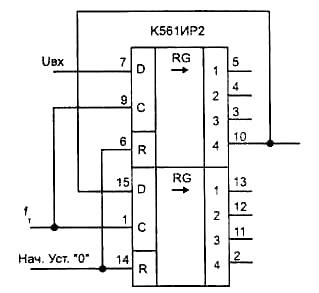

Фиг. 1.59. смяна регистър

Пример метод за производство на цифров забавяне използване на сменящ регистър е показано на фиг. 1.59.

Забавянето зависи от изхода и е синхронизиран с генератор тактова честота (последователно произволен брой регистри могат да бъдат включени). В присъствието на нивото на дневник. "1" на входа на D при нарастващ фронт на импулси, идващи от генератор Тай часовник, протоколът е написан на регистъра.

В следващия часовник цикъл е стойност на сигнала да е последователно на изхода на регистъра. Подобна схема може да въведе грешка в изходния сигнал на не по-дълъг от срока на часовника продължителност, и се отнася и за малко закъснение. За по-нататъшно забавяне сигнал понякога е по-икономичен е използването на RAM чипове заедно с контролната верига (чете и записва през изисква интервал).