Графичен дизайн или текст Verilog / VHDL?

Аз смея да докосне такова holivarnuyu Заглавие: сравнение на два метода за развитие, графичен схема вход и текстово описание на проекта на HDL Verilog / VHDL езици.

Кой метод е по-добре?

Аз трябва да кажа, че аз съм привърженик на влизането на текста, така че със сигурност ми забележка може да изглежда предубеден. Независимо от това, ето още важни забележки по този въпрос:

- проект може да бъде изпълнен както и замислено, независимо кой метод се използва, само като лош дизайн може да се направи с помощта на верига представителство в описанието на Verilog / VHDL. Това означава, че качеството на проекта по-скоро зависи от уменията на програмист от избрания инструмент (въпреки че програмистът може да има свои собствени предпочитания и специфичен опит с развитие на околната среда).

- независимо от представянето на проекта под формата на текст или HDL диаграми, компилаторът (на теория) следва и трябва да се синтезира по същия оптималния начин за фърмуера в FPGA. Във всеки случай, компилаторът ще оптимизира комбинаторни логика изтриване неизползвани елементи, спусък, синтезира и да оптимизира Netlist.

Сега нека да разгледаме всички същите предимства и недостатъци на развитието на методи в схемата или в текстов вид.

Обикновено има няколко взаимосвързани критерии за оценка на дигитални проекти за разработване на метод за FPGA и ASIC: удобство, бързина на развитие, производителност, преносимост, код управляемост и надеждност.

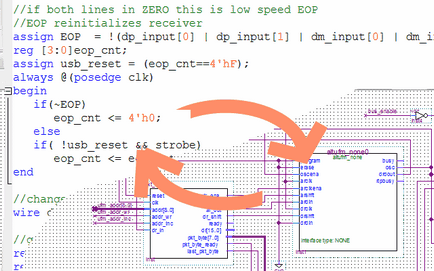

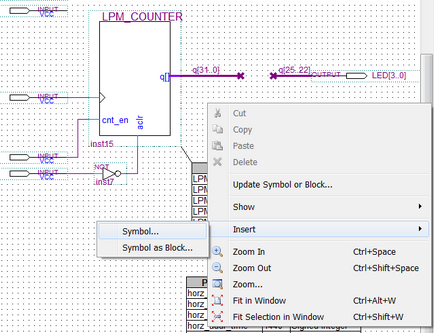

Е, в Кварт II среда за схеми за рисуване не е опция. Ако искате да добавите нов компонент към веригата, е необходимо за изпълнение на последователност от действия, като "кликнете с десния бутон" => избор в менюто Insert => Символ на => по-късно в селекцията на диалогов прозорец, в списъка на библиотека примитивен => го инсталирате на веригата. Тогава все още понякога искате да редактирате свойствата на избрания елемент, а това е отново мишка, диалогови прозорци, а след това, след много часове работа с мишката - ". Тунел синдром" болест на страна,

Колко движения с мишката и колко кликвания, което трябва да направите, за да добавите нов елемент към схемата в Алтера Кварт II среда?

Разбира се, скоростта на развитие е тясно свързано с удобството на проектиране на околната среда (виж първа точка).

Обикновено хората, които рисуват схема казват, че не ми пука за тяхната скорост, защото мисля за проекта отнема много повече време, отколкото си рисунка. Вероятно това е така, това може дори да се съгласи.

В действителност, аз често се използва графичен вход. Често в проекта, което имам е един графичен файл на йерархията на най-високо ниво. Допълнителни модули са включени в йерархията на една от Verilog, всички компоненти създаден съветника тип Altera FIFO, компонент контролер на DDR, SRAM модул или PLL, е нещо друго. Опростен дизайн и може да се направи, но той постепенно става по-сложно с времето, за да редактирате става по-трудно и по-трудно. Ние трябва да натиснете графичните обекти, компоненти, кабели, гуми, за да вмъкнете нещо ново. Тази схема, движение обекти отнема много време, особено ако проектантът има чувство за красота, и той обича веригата с елементите подравнени решетка. Това може да се случи, че вместо да работи по собствените си проекти хора, работещи върху движещите се компоненти. Печат голям графичен дизайн на принтера става все по-трудно, формат А4 не е подходящ, трябва да А2 и А1 или залепете чаршафите.

В допълнение, трябва да се отбележи, че скоростта на развитие е силно зависимо от специфичните езикови програмиране особености или дизайн околната среда.

И един важен момент: всичко, което може да се направи във веригата може да се опише с текст език HDL един, но не всички, от това, което е описано в езика на HDL могат лесно да бъдат приложени във веригата. Ето някои примери:

модул hvsync (

// входове:

въвеждане на тел pixel_clock,

// изходи:

изход рег Hsync,

изход рег вертикалното синхронизиране,

);

// видеосигнала на параметрите, по подразбиране 1440x900 60Hz

параметър horz_front_porch = 80;

параметър horz_sync = 152;

параметър horz_back_porch = 232;

параметър horz_addr_time = 1440;

параметър vert_front_porch = 3;

параметър vert_sync = 6;

параметър vert_back_porch = 25;

параметър vert_addr_time = 900;

.

- Друга важна характеристика на дизайна в текста на Verilog HDL - това е възможност на условията компилация проект. Например, номер на проекта, фрагмент Амбър (ARM-съвместим процесор и система на чип).

i_irq (amber_irq),

.i_firq (amber_firq),

o_wb_adr (m_wb_adr [1])

.o_wb_sel (m_wb_sel [1])

.

Проектът може да се вмъкне, съставили 5-фазна процесор (по-бърз, но отнема повече логика) или 3-степенна процесор (по-бавно, но заема по-малко логика). И това условията компилация се извършва, в зависимост от конкретния настройка AMBER_A25_CORE. Не можете да използвате условията компилация в схемите. Условна компилация е необходимо, когато проектът има редица варианти, например, за различни видове FPGAs за подобни проекти, които да бъдат включени в проекта за модул за отстраняване на грешки, че крайният продукт не е включен и така нататък.

- Третият пример - използването на специални структурни Verilog HDL език, които позволяват да се генерират и го поставете във проекта свързани случаи на други модули на. Например, тук е поглед към кода в Verilog:

модул inst_loop

(

въвеждане на тел часовник,

вход проводник,

тел на изход

);

genvar индекс;

генериране

за (индекс = 0; индекс <4; index=index+1)

започне. фу

тел o_q;

ако (индекс == 0)

# функция (индекс) func_inst (

.fclk (часовник),

.г (в),

.Q (o_q)

);

още

# функция (индекс) func_inst (

.fclk (часовник),

.г (фу [индекс-1] .o_q),

.Q (o_q)

);

край

endgenerate

присвоява от = фу [3] .o_q;

endmodule

езикова конструкция генерира-endgenerate ви позволява да зададете желания брой копия функционален модул и ги свързват един с друг, както е необходимо. В допълнение, всеки екземпляр от функционален модул също могат да бъдат параметризирани да "знаят мястото": в този пример, # (индекс) - тя премина параметър модул позиция и поведение модул може да зависи от този параметър. Горният пример прави точно такава схема:

Този цикъл може да се създаде, например, структурата 1000 свързан модули. Как да се направи това, за да веригата? Колко време ще отнеме? И изведнъж ми нарисува схема, и тогава ще трябва да добавите сигнал към модула, че всички повторно-Fix преначертае? Тя ще бъде трудно.

Налице е и аргумент в полза на графични файлове - видимост. Човекът твърди, че настоящата схема и да го приложи като идея по-лесно да планирате. Какво има да се спори? Предполагам, такава схема, но аз веднага мога да го опиша в Verilog. Всъщност, аз вярвам, че човекът, който пише на Verilog / VHDL трябва незабавно да представи себе си в кръга на главата е описано в текста - това е правилно и трябва да бъде.

За съжаление, аз трябва да кажа, че лично аз имам много често има проблем с четенето на схеми. Ето един пример.

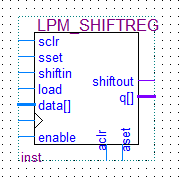

Виждам в схемата трябва LPM_SHIFTREG стандартен компонент на графичната бибилиотека Алтера Кварт II. Кой може да каже това, което току-що сигнал има по-висок приоритет sclr или товар. Какво се случва, ако и двамата се активират? Тя може да бъде записано в регистъра на всички нули, или ще се зареди нови данни в регистъра за смяна? Така че аз забравям. Аз гледам на този компонент във веригата, и не може да си спомни какво означава всичко това. Предполагам, че имам малко опит с схеми ..

С verilogom по-лесно. Не алегоричен:

рег [7: 0] serial_send_reg;

винаги @ (posedge CLK)

ако (sclr)

serial_send_reg <= 0;

още

ако (натоварване)

serial_send_reg <= next_data;

още

serial_send_reg <=

В описанието на Verilog HDL сигнализира приоритети веднага видими в текста.

Като цяло, през визуалното представяне на проекта Аз лично нямам предпочитания към схеми.

Преносимост и преносимост на проекти.

Мисля, че това е ясно. Ако програмист иска да се развива тя може да се използва никъде другаде, освен в своята FPGA, тогава той трябва да използвате текстови описания на Verilog / VHDL. Случило се така, че няма единен стандарт за описване на графични файлове, цифрови схеми днес. Оказва се, че си Altera изображение файлов формат, а Xilinx собствени. И производителите на ASIC чипове няма да влязат в графичен дизайн, ще бъде работата на само текст.

Ние за нашия съвет Marsohod2 Амбър е пренасянето на проекта с отворен код с opencores - то е било извършено първоначално за чипсет Xilinx на езика на Verilog HDL. Сега можем да го компилирате за FPGA Altera циклона III. Ако няма да има проект е под формата на графики, мисля, че няма да има шанс.

По принцип схемите за визуализация - това е целият проблем. Ако е необходимо да се покаже вашия проект като схема на някои експерти, първото нещо, което трябва да направи - себе си зададете среда за разработка, и да започне да се изпомпва от Интернет инсталационния пакет размер на 3-4 GB на. И това не се изпълнява или не, ако човек не си струва много често операционната система на компютъра. И ако аз съм на път и аз имах с него само Ipad или Galaxy Tab? Текстът все още е възможно да се види, но схемата е трудно.

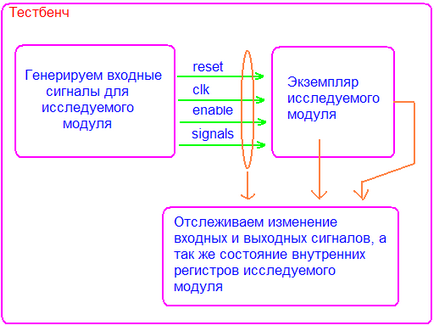

Важен елемент от процеса на развитие на цифрови схеми - Проверка. Казано по-просто - това е моделиране на проекта или на неговите модули. В случай на текст процес проекти тестване е, както следва: отделна програма, написана-Testbench. Testbench програма е написана на същия език като този на самия проект. Например, проектът е разработен в Verilog. Testbench може да се направи в Verilog.

testbencha програма разглежда готовия модул като черна кутия, всички от входните сигнали за черната кутия симулира, всички изходи на устройството за изпитване, което наблюдаваме и ще видите, че те са по предназначение. Ние програмираме въздействие към модула за изпитване и контрол на отговор. Има много инструменти за такава проверка. Фирма Altera доставя с неговия проект среда ModelSim Алтера Кварт II по околна среда - просто да се симулира Verilog / VHDL дизайни. Налице е проект с отворен код за Икар Verilog функционална симулация проекти. Аз го използвам много често - много прост инструмент.

Интересно е, че много от производителите да предоставят чип Verilog модели на своите чипове, за да направи по-лесно за разработчиците да отстраняваме проекти.

Има много добри примери за симулация проекти на нашия уебсайт. Например, ние се симулира системата на чип Амбър и стартирате операционната система Linux в системата. Това е един много сложен симулация, той включва модел на SDRAM памет, самата система върху чип с процесора, на bootrom, сериен порт, таймер, прекъсване контролера. По време на симулацията, анализира процесора изпълнява милиони инструкции. Ясно е, че такава дългосрочна симулация обхваща практически всички възможни вътрешни състояния на системата. Надяваме се, че проектът работи правилно.

На нашия сайт, дори и след като направи преглед на симулатора на Кварт II v9. Това беше много отдавна. В по-късните версии на Altera дизайн среда симулатор изключени от пакета. Ами истината е, че не е много добра.

Какво да правя сега? Има само един начин да се симулира верига в kvartusa среда. Отворете схема файл и след това в досието на меню => Създаване / обновяване => Създаване на HDL дизайн на файла от настоящия файл. В резултат на схемата се превръща в текстов файл на езика на Verilog или VHDL. Е, след това, подобно на всички други хора - използвайте ModelSim.

Не е удобно, има допълнителна междинен стадий на реализация. Ако множествена правилната схема и да го превърнете в симулация, а след това дори може да се превърне в мъчение.

Това често се случва, че някои необходима функция, след като е работил, а след това изведнъж спря. Защо? Защо? Кога и който е направил корекции в проекта? Как да следите промените в проекта във времето?

Проектите на софтуера при C / C ++, C #, PHP, Python, както и всички други, за да се поддържа на проекта използва сървър за съхранение източник. Типичен пример на система за контрол на източник - тази система Subversion или GIT. Тези системи позволяват да се направят промени в проекта на кода и спести междинните състояния на проекта. Възможно е също така да се разклони на проекта, проектът работи слее клоновете в основния поток на проекта и така нататък. Може би по някое време трябва да се намери кой и кога и защо да се направят някои промени, може да се наложи да се върнете към предишна версия на проекта. Само за използването на системи за контрол на версиите ви позволява да се поддържа голям десен проект.

Всичко това, разбира се, се отнася и за текстови описания на хардуерни проекти в Verilog / VHDL.

Пример за нашите проекти в система за контрол на версиите - кехлибарено-Marsohod2 - пренасяне система на софтуера с отворен код Амбър pristalle картата Marsohod2. Целият процес на пренасянето е в публичното пространство на GitHub. И това е страхотно.

Ако използвате текстови файлове е много лесно да се сравняват различни версии на един и същ модул. Можете просто да утеши разл команда в Linux. Или има средство за сравняване и обединяване текстови файлове тип Meld.

Но кажи ми как да се сравняват двете схеми: малко по-голям и по-малко повече от един нов? Не знам. Поради липсата на средства за сравнение на схеми графични използват VCS става много проблематично и неудобно. Тук е още и значителен аргумент срещу схеми.

Заключение мога да го направя. Използването на текст, за да опишат хардуерни проекти в много случаи за предпочитане. входното изображение средства могат да бъдат веднъж и да се върнат, но само ако и когато няма да има стандарти за схеми за съхранение и инструменти за улесняване на техния принос схеми за контрол и сравнения.