Провеждане на асинхронен сериен комуникация с външно устройство, се усложнява от факта, че предаващата и приемащата страна на сериен връзка, използван настроен на същата честота, но физически различни часовник импулсни генератори, а оттам и цялостната синхронизация отсъства. Вземем примера на организацията контролери серийни интерфейси за сериен асинхронно предаване и приемане на информация.

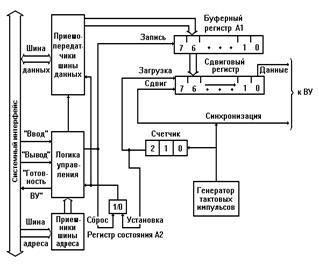

Обикновено контролер за асинхронен трансфер на данни в роб на серийна комуникация линия е показано на фиг. 3.8. Тя е предназначена за предаване на данни във формат, с два стоп бита.

Фиг. 3.8. асинхронен сериен предаване контролер

След предаване на следващия байт данни в статута регистрирате A2 записва 1. Изходът за единица регистрирате A2 информира процесора на контролера на готовност, за да получи следващия байт данни и предаването му върху връзката на комуникациите в роб. Това забранява един и същ сигнал пулс оформяне схема за генериране на смени импулси - разделител часовник сигнал генератор 16. Броячът на промяна на честотата на пулса (Брояч на Министерството на отбраната 10) е в нулево състояние и неговата единица изходен сигнал се подава към врата, и подготовката поколение късо съединение на товара сигнал за смяна регистър ,

В процеса на прехвърляне на един байт данни започва с факта, че процесорът, изпълняващ команда "Изход", поставя байт на трансфер на данни. Едновременно с това, CPU създава система за контрол интерфейс сигнал "изход", които са произведени чрез записване на предава байт в буфер регистрирате А1, А2 състояние регистър изчисти и формиране на портата и сигнал "Load". Предадените байт съответства на 8 бита на регистъра за смяна 1, нула разряд смяна регистър пише 0 (започнем малко) и в нивата 9 и 10-1 (стоп бита). В допълнение, отстранява сигнала "Reset" от честотния делител, тя започва да се натрупват импулси и тактовият генератор генерира импулс смяна в момента на получаване на шестнадесети часовник пулса.

На изхода линия контролер "Данни" поддържа състояние 0 (стартов бит стойност) за толкова дълго, докато първата смяна пулса се развива. промяна на импулса се променя състоянието на изместване на тезгяха пулс до нула и презаписва етап от регистъра за смяна, първият бит данни, предавани байта данни. Състояние, съответстваща на стойността на този малко ще се поддържа по линия "данни" към следващата смяна пулса.

По същия начин, останалите битове информация, която се предава, първата спирка бит, и накрая, на втория стоп бит, предаването, чиято смяна импулсен брояч отново да се настрои на нула държавата. Това ще доведе до поста 1 в регистър статут А2. Един единствен сигнал A2 от изхода на регистър забрани срязване формация импулси, а също така информира, че процесорът на готовността да получи нов байт данни. След приключване на следващото предаване рамката (стартов бит, две информационни байта и да се спре бита), контролерът поддържа връзка логическо ниво и една (стойността на втория стоп бит).

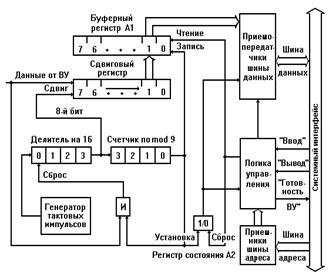

Фиг. 3.9. Получаване на асинхронен сериен контролер

логика едно ниво по линия "Данни" до контролер асинхронно рецепцията на данни (фиг. 3.9). Това ниво се създават условия за генериране на сигнал, който забранява експлоатацията разделител честота часовник осцилатор. Наистина, след прием на предходната байт данни смяна импулсен брояч (брояч за мод 9) е в нулево състояние и врата, и получава две единични сигнали: да се премине от тезгяха и линията "данни". На изхода на логическия елемент произвежда сигнала за рисет на часовник сигнали честота делител, забраняващи формирането на импулси на смени.

В момента на промяна на стоп бит, за да започнете малко (началната предаването на нова рамка) на ред "Данни" логика нула ниво и по този начин ще бъдат изтеглени от нулиране сигнал честотния делител. Състояние 4-битов двоичен брояч (делител на честота) започва да се движи. Когато броячът натрупаната стойност 8, тя ще издаде сигнал към входовете на регистъра за смяна и брояча на промяна на пулса. Тъй като честотата на сигнала импулс на приемника осцилатор трябва да съвпада с честотата на часовника на предавателя, преминаването (четене) бита се намират при средния интервал от време отделено за предаване на бита данни, R. Д., необходима за генериране на шестнадесет тактови импулси време. Това се прави, за да се намали вероятността за грешка поради възможен генератор разлика честота предавател и приемник, нарушаването на предаваните сигнали (преходни) и т. Н. Следващата промяна ще настъпи след преминаване на шестнадесет тактови импулси т. Е. В средата на време интервал на предаване на първата информация малко.

Когато се приема в регистъра смяна на деветия рамка бита (осем бита данни) от него "изскача" започне малко, и следователно, цялата получена байт данни се поставя в регистъра за смяна. По това време, брояча на смяна пулс стига до нула държавата и нито един сигнал ще бъде излъчен на изхода, на която съдържанието на сменящия регистър могат да бъдат пренаписани в регистъра на буфер, за състоянието на регистър A2 е написано едно и тя ще информира процесора на завършване на получаване на следващия байт, врата, и се подготвят за формиране на сигналите "Reset" (този сигнал се формира след пристигането на първата спирка малко).

След получаване на готов сигнал (1 в регистър А2), процесорът изпълнява командата "Enter" (вж. Пример 2.2 паралелно предаване на данни). По този начин генерира управляващ сигнал към интерфейса на системата "Enter", които са произведени чрез изпращане на получените байтове данни от регистъра на буфер в процесора (сигнал "Четене") и нулира регистър статут А2.

Имайте предвид, че за простота, контролерът на фиг. 14 не показва веригата за управление на стоп бита на приетия пакет. Не се показва също са схеми или нечетност (паритет) информация, която се предава (обикновено в предава байт на осмия бит се дава стойността 0 или 1, така че байт е четен брой единици). В реални контролери са такива схеми, и ако администраторът не приема желаната връзка броят на стоп бита или генерирания сигнал паритет грешка на схемата за паритет, получените данни в прозореца, в бита се игнорират и контролера чака ново начало малко.

Комуникация с роби от серийни комуникационни линии са широко използвани в микрокомпютър, особено в случаите, когато не се изисква висока скорост на комуникация. Въпреки това, използването от тях на последователни линии, дължащи се на роба поради две важни причини. Първо, серийни комуникационни линии са прости в тяхната организация: две жици с симплекс и полу-дуплекс предаване и най-много четири - с дуплекс. На второ място, във външното устройство с помощта на микрокомпютъра, с когото трябва да се направи обмен в последователен код.

В се използва модерна микрокомпютър, обикновено, универсални контролери за пореден BB предоставят както синхронни и асинхронни обмен на данни с подчинен режим.

Свързани статии