Наскоро, добре известен китайски сайт предлага да купи всички видове шунки дъски за оценка на FPGA. но за съжаление, че е на разположение за неподготвен ума (или този, който ще бъде приятен за мен) описанието на руски (Как работи това?) в интернет, аз не съм намерил. В крайна сметка, разбира се, на разбирането на това, но това е също един вид и желание да напише уводна статия с красиви снимки, които биха ясно обяснени същността на FPGA. Нека да започнем.

FPGA - Поле програмируеми логически интегрални схеми. ВАЖНО! Има два вида на LSI (Large интегрална схема), която имаме в страните от ОНД отговарят на определението за FPGA, но въпреки това, на принципа на работа на LSI е различна, което създава някои дисонанс с реалното състояние на нещата. В същото време на Запад във всяка от LSIS има доста от свое име, като ясно се комбинират Магия, а именно: CPLD-чип - един FPGA фърмуер (конфигурация) винаги се съхранява в себе си и силата чип е изключен НИКОГА изтрита. Изглежда доста логично, че самостоятелно пиърсинг трябва да се съхранява в чипа, и да се съсредоточи върху него не трябва да бъде, но се премести към следващото LSI. FPGA чип - това също е FPGA, но конфигурацията му се съхранява във външната енергонезависима памет източник (например всякакъв вид флаш). Как става това? Много просто, всеки път, когато включите, конфигурацията на FPGA се шие, която е взета от паметта и се изтрива при изключване.

Трябва да се отбележи, че процесът на записване в CPLD конфигурационния и FPGA е по-различно: всички писмено описание език VHDL или Verilog хардуера. Тогава там е синтез и изпълнение (съставител първо ще се опитаме да разберем това, което сте написали, и след това се опитва да постави всички структури, регистрите и връзки в FPGA, написан въз основа на), а последният етап се генерира .bit - файл, който се шие от интерфейса JTAG-програмист устройство.

Ако CPLD все още някак си свикнали да работят ( "Е, как в микроконтролера!" - да ви кажа), а след това на FPGA, със своите непонятни външни източници памет, изглежда някои неудобни звяр, така че всичко по-долу е писано ще бъде посветена на FPGA (но трикове програмиране валидна за CPLD), да се направи малко повече светлина по този въпрос. Всички примери код ще се изпълняват на езика VHDL.

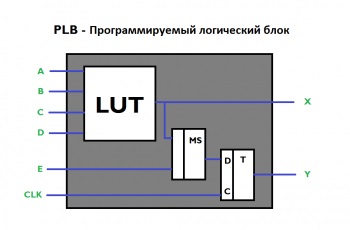

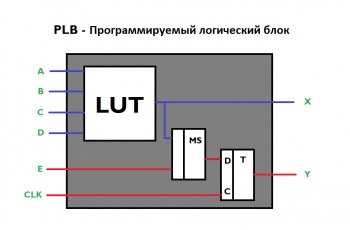

Помислете за най-малкия компонент FPGA, който се нарича PLB - програмируем логически елемент.

PLB състои от LUT маса на кореспонденция, и мултиплексор D-тригер. Помислете за началото на сравнителната таблица. В действителност, LUT - статична памет с произволен достъп (RAM -. Оперативна памет е енергонезависима памет, която се изтрива, когато данните за електроцентрали (включително Записано Off On отново, както и всички записани данни се изтриват) има висок процент на ..... скорост.), който съхранява изходни стойности на X, образувана стойности а, в, с, D.

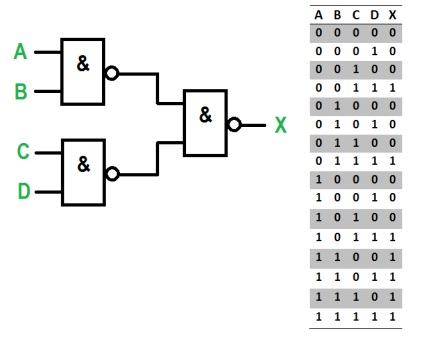

Да предположим, че искаме да се приложат в FPGA схема е показано на фигурата по-долу, със съответния истина таблица:

Сигнали А, В, С, D, се подава към вход LUT, след това се излезе от таблицата на истина, която се съхранява в LUT, образуван мигновено сигнал X. Това е много проста. В кода, то изглежда така:

X <= (A nand B) nand (C nand D);

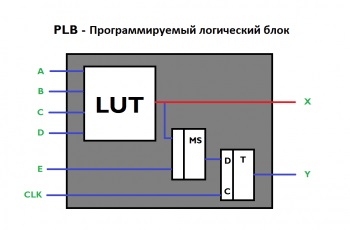

Фигурата по-долу показва червената линия като изходен сигнал на хардуерно ниво:

Но какво, ако ние трябва да се синхронизира сигнала часовник честота? След това, по време на конфигурацията на писане, трябва да се уточни, че изходния сигнал ще бъде инсталиран или на лицевата страна (rising_edge (CLK)) или парче (falling_edge (CLK)) на CLK на часовника сигнал и компилаторът ще се изходния сигнал в X изход, изход Y. в език VHDL тя изглежда така:

ако (rising_edge (CLK)), тогава

Y <= (A nand B) nand (C nand D);

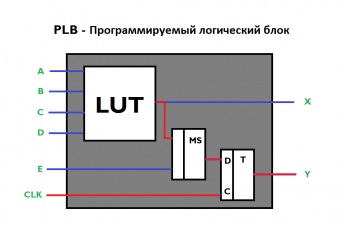

На ниво хардуер, това се случи, както следва: сигналът от LUT е спусъка за Т, която определя изходната стойност У на CLK на.

Какво да направите, ако искате да се забави на входния сигнал от един цикъл? След това, в конфигурацията си поставихме на сигнала, за да бъде задържан, новият сигнал по време на синхронизиран на CLK:

ако (rising_edge (CLK)), тогава

Хардуер това се случва по следния начин:

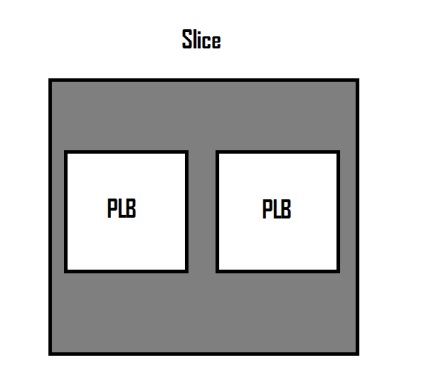

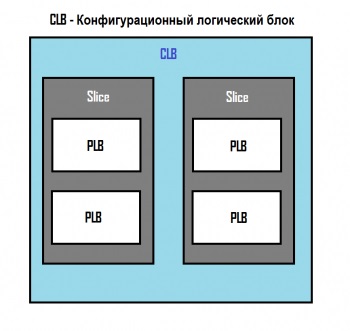

Нека ви напомня, всички по-горе трябва да бъде в рамките на най-малко един компонент FPGA, а именно PLB. Но вътре десетки FPGA хиляди PLB (а може би стотици, те са технология, която не стои на едно място), които могат да бъдат свързани помежду си. За улеснение на организация на връзките между тях, в FPGA се използва модулен подход: малки е голяма, две PLB форма едно парче.

В заключение бих искал да ви кажа защо трябва да погледнем в FPGA, и по-специално на FPGA чипове. На първо място, това е неограничено поле за творчество: имате нужда от екзотична 13-битов таймер / брояч? - получи. Изисква 15 UART? - лесно. пренос на данни при скорост от 6 Gb / и? - няма съмнение. И ако ползите от FPGAs са ясни, след това преминете към някои от тях е за предпочитане: CPLD или FPGA? Трябва да се отбележи, че всъщност всичко зависи от приложението. Ако проектът не е голям, но това изисква по-специално периферна, то CPLD. И ако имате нужда от гъвкавост и много висока скорост, това FPGA. Нищо не ви пречи да го направят в някакъв момент от времето FPGA работи за първи път в една версия, но след това във второ, трето, пето, десети (конфигурируеми свойства), тъй като за разлика от други чипове, запис на ресурсите / изтриване на FPGA са склонни да безкрайност (когато за последен път сте променили RAM в компютъра ви се дължи на факта, че тя се развива ресурс на отписването / изтрие? това е, което аз знам. Всъщност това е всичко, благодаря ви за вниманието

Тук съм за вашата връзка, вижте минималната системна платка, за да го настроите ALTERA FPGA CycloneII EP2C5T144. Така че, това, което съм, за използване на тази карта трябва да го свържете към външен чип флаш памет? Или фърмуер baytblasterom ще трябва да изтеглите при всяко включване на борда, и че ще работи преди прекъсване на захранването, без външна памет?

На повечето дъски оценка вече имат чип с памет, който ще съхранява на фърмуера, така че Вие лично не разполагат с паметта спойка. Що се отнася до процеса на светкавица, когато шият, околната среда ще ви предложи да изберете къде да изтеглите фърмуер: в чипа на FPGA или FLASH чипа. Ако заредите FPGA, тогава да, захранването е изключено фърмуер ще бъде изтрит, ако FLASH, а след това захранването е изключено по време на фърмуера ще започне да мига, а дори и при повторно стартиране FPGA себе си ще се зареди на фърмуера от FLASH, без помощта на ByteBlaster'a.

За отговорът трябва да знаем в какъв размер да купя, който имате.

Но като цяло, за самите начинаещи мога да препоръчам просто като нормална на FPGA, CPLD, и не повече или по-малко от сегашното поколение, например,

Като за начало, по-добре от Altera, те имат по-адекватен софтуер и ясно.

Свързани статии