1. Класификация на елементите и компонентите на компютъра.

Компютър може да се представи като съвкупност от възли и всеки възел - като съвкупност от елементи.

Елемент - най-малката функционална част, която може да се раздели на компютри в логическа дизайна и техническото изпълнение.

По функционално предназначение компютърни елементи могат да се разделят на:

- логика (един за реализиране булеви функции);

- памет (за съхранение на един-битова двоична стойност);

- спомагателни (за образуване и генериране на импулси, таймери, индикатори елементи ниво конвертори и други подобни).

В зависимост от вида на сигнала:

Чрез представяне на входните и изходните сигнали:

Възел - набор от елементи, които реализират изпълнението на една от операциите на машината.

Има два вида на компютърни компоненти:

- натрупване (с памет).

От друга страна, комбинаторни единици съдържат разширители, сравнение схеми, енкодери, декодери, множители, програмируеми логически масиви и т.н.

Натрупват единици - джапанки, регистри, броячи и т.н.

В цифрови устройства, променливи и съответните сигнали не се различават непрекъснато, но само на отделни моменти от време. Интервалът от време между съседни точки от време се нарича такт.

Информацията в компютърни елементи могат да бъдат обработени по сериен или паралелен код. В последователен код всеки път, когато цикълът за един бит текстообработка. В този случай, всички части от думи са записани в друго от същия елемент.

Когато паралелна обработка на кодови думи не са разположени във времето и в пространството, като стойностите на всички битове се обработват едновременно в един цикъл.

Компютърна 3-то поколение са базирани на основните логически елементи (LE). Например, NAND или NOR. Най-важните характеристики на всеки основен елемент логика е консумацията на скорост и сила. В зависимост от мощността на разсейване се разграничат следните LE:

-mikrovatnye F до 300 MW;

- тънък P до 3 MW;

- средната мощност от 30 MW за Р;

- P-мощен от 30 MW.

От средната време забавяне на LE са разделени на групи:

- ниска скорост TD> 50 NS. P = 0.01-1 MW;

- TD = средна скорост от 10-50 NS. P = 10.1 MW;

- висока скорост TD = 5-10 НЧ. P = 10-50 MW;

- свръхвисока TD производителност <5 нс. Р = 50-1000 мВт.

Освен Всяка LE характеризира със стойност на напрежението

съответните нива на логика '' 0 'и' 1 '. комбиниране на съотношението между входния коефициент fanout.

LE са обединени в групи (серия) на интегрални схеми, например, K155 серия. K500. K176 и др.

За всички, подобряване на постиженията PE е съпроводено с увеличаване на консумацията на енергия и увеличаване на плътността на разполагането на елементи на чип - спад в производителността.

Адер. За да разберем принципите на изграждане и експлоатация на суматора разгледа пример за добавяне на двоични числа:

Всеки ранг и един-битов ехидна трябва да формират сумата Si и прехвърлени на MSB.

Разграничаване половин разширители HS (игнорира пренасяне на сигнала) и пълния ехидна SM (отчита пренасяне на сигнала).

Half-ехидна мулти-битов пълен ехидна

Kodepreobrazovatel - комбинаторни блок (CU) като м входове и изходи п, и преобразува входните т- битови двоични числа в изхода n- малко. Най-често използваният тип 2 - кодиращи и декодиращи.

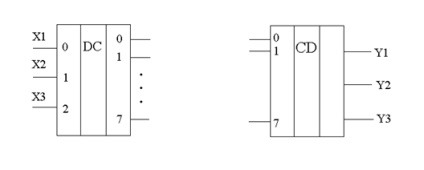

Декодер (DC) - KU е -Log и м изходи, които са '' 1 '' само на един от изходите, което съответства на десетично число знак вход комбинация. LH работа е дадена таблица истина.

Енкодер (SD) - решава проблема обратен даден по-рано.

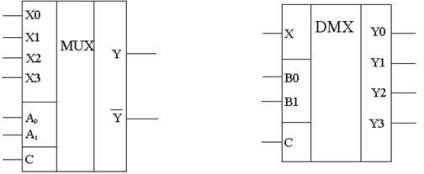

Демултиплексор (DMAC) решава проблема с обратен.

Определяне MUX, DMAC е дадена по-долу:

Programmable Logic Array - Universal комбинаторни схема за преобразуване на вход n- битов двоичен код изход т- битов код на дадена таблица истина. Широко използвани в контролните микропроцесор единици.

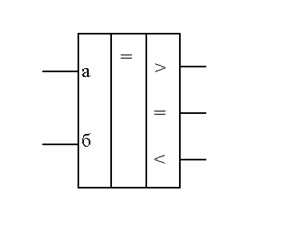

сравнителни схеми - необходими за организацията на разклоняване за обработка на данни и т.н. (Вж. Фиг.).

3 Възли акумулатор тип.

Както елементи компютър за съхранение, използвани тригери или устройства на базата на магнитни материали.

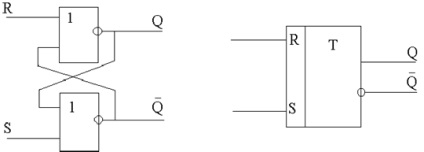

Trigger - държавна машина, която има две стабилни състояния и под влиянието на промените, контролните сигнални от едно състояние в друго.

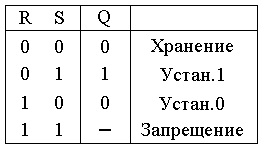

Чрез функционалност разграничат RS. Т. Дж. D - задейства комбинирани RST-задействания. JKRS. DRS -triggery т.н. В този означения S. R - входове за отделна инсталация флоп на "1" (S) и "0" (R).

Т - преброяване спусъка вход.

J, К - входове за отделен монтаж на Жк тригер на "1" (J) и "0" (к).

D - вход за тригер на държавата "1" или "0" с време на закъснение по отношение на момента на настъпване на информационния сигнал.

C - часовника вход.

Дефинирани условието за задействане Q сигнал при прякото му изход. закони експлоатация Trigger определени входни маса преходи от компактен, при който колоните състояния могат да се показват, че новата държава е едно и също с предходната, или е отрицание.

Разглеждане на RS - тригер. Asynchronous (не часовник) RS - тригер на интегралните елементи, или - не са показани на фигурата:

А спусъка се образува от 2- или елементи - не е свързан така, че положителна обратна връзка, чрез която изход транзистор на една от веригите в стабилно състояние или - затворено и друг отвори.

Експлоатация на RS-тригер може да се опише с израза:

работа Качество задейства оценява основни параметри - като например скорост, капацитет на натоварване, консумацията на енергия, шум имунитет.

В допълнение към RS-тригер вход съвпадение верига, е възможно да се изгради всякакъв вид тригер.

За да можете да синхронизирате възли и компютърни устройства, използващи синхронни тригери, които имат специален вход за часовника. Ако отговорът на въртящия момент на асинхронен спусъка, прикрепена към смяната на времето в нивото на входния сигнал, синхронните - часовникът време на разположение.

Висока ниски тригери се избягват повреди при писане или четене на информация в един часовник цикъл: на първия етап, извършва запис на предния фронт на импулс, а вторият - издаване (пренаписване на втората стъпка) с падащ фронт.

Т - спусък променя състоянието си при пристигането на всеки импулс, т.е. той ги смята. Използва се за изграждане на броячите.

Регистри. Предназначен за записване, съхранение и превръщането им в двоични числа. В тригер се използва, който може да съхранява един цифри двоично число като регистър единица клетка. Писането и четенето на информация в регистъра може да се извърши последователно (побитовото) или паралелно (всички битове в даден момент). Съответно се прави разлика регистри сериен, паралелен, сериен към паралелен, паралелно към сериен и универсални.

Counter. Функционално устройство за преброяване на броя на получаване на своите входни сигнали (импулси) и записване на резултата под формата на мулти-битова двоична брой.

Стойки са разделени на сумирането, изваждане и обратимо.

Свързани статии