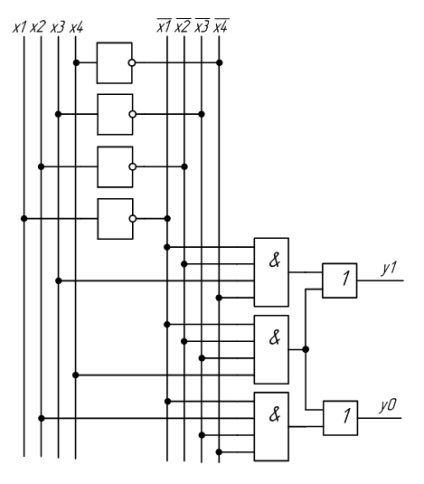

Синтезира енкодер. За да направите това, пишем на системата на собствените си функции:

Y1 = x1 · х2 · x3 · x4 + x1 · х2 · x3 · x4

Y0 = x1 · х2 · x3 · x4 + x1 · х2 · x3 · x4

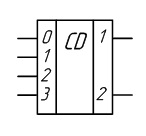

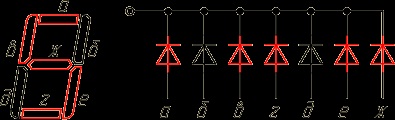

2.3 код конвертор за показване седем сегмент

Най-широко известни транскодерите да включват цифрови показатели. Например, инвертор 4-цифрен позиционен двоичен да е десетична. Има дисплей седем сегмент и да го използвате, за да маркирате нужните десет цифри.

Очевидно е, двоичен код трябва да има най-малко 4 - х бита (2 ^ 4 = 16, което е по-голямо от 10). Построяване на масата истина на действие на такъв преобразувател.

Таблица 2.3 - Таблица Converter истина

Според TI е лесно да се създаде система за eigenfunctions за всички изходи, т.е. PDNF, минимизиране на това и да се създаде концепцията.

В цифрови схеми, необходими за работа с помощта на клавишите логическите нива. Затова е желателно да изберете устройство, което може да изпълнява функцията на електронното ключ за контрол на цифровия сигнал. Опитайте се да "принудят" да работят в познатите логически елементи, както и електронен ключ. Помислете за TI логически елемент "И". По този начин един от входовете на NAND порта "И" ще се разглежда като електронен ключ информацията за вход и още един вход - като контрол. Тъй като и двата входа на NAND порта "и" равностойни, а след това няма значение коя от тях е контрол на входа. Нека X е входен контрол, и Y - информация. За улеснение на дискусия ще се раздели на две части TI зависимост от нивото на логиката на сигнала при входящ контрол X.

Таблица 2.4 - истина маса

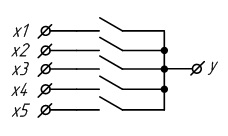

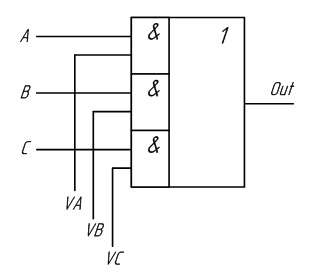

Според таблицата на истината ясно показва, че ако входа на контролния X подава сигнал с нулево ниво логика се прилага към входа към изхода Y Out неуспешна. Когато се прилага към контролния вход X логика един сигнал към входния Y, се появява на изхода Out. Това означава, че логиката елемент "Аз" може да се използва като електронен ключ. Няма значение кой от входния елемент "И" ще се използва и като входен контрол, и които - като информация. Остава само да се комбинират резултатите от елементи "и" един общ изход. Това се прави с помощта на "ИЛИ" логическия по същия начин, както и в изграждането на схемата върху произволна маса истина. Получената вариант на прекъсвач верига с контролни нива логически е показана на Фигура 2.8.

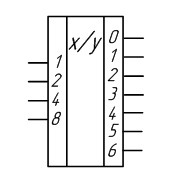

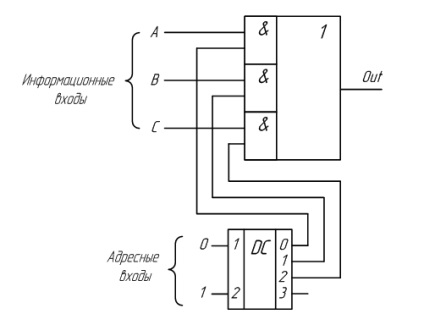

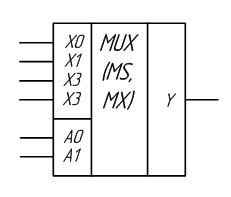

Веригите показани на Фигури 2.7 и 2.8, може едновременно да съдържат няколко входа за един изход. Обикновено, обаче, това води до непредвидими последици. В допълнение, това отнема много входове на мултиплексора така обикновено включва двоичен декодер за контролиране на такова преминаване, както е показано на фигура 2.9. Тази схема позволява да се контролира превключване на входа мултиплексор с данни посредством двоични кодове, прилагани към своите управляващи входове. Броят на въвеждане на данни в такива схеми избран кратно на степен на две.

Особености на multiplesorov реализация в Verilog език могат да бъдат прочетени в статията:

FPGA архитектура. Част 2. мултиплексор

Адер - компютърна единица за добавяне на двоични числа. Изграждане на двоични разширители са обикновено започва с ехидна модул 2.

Modulo-2 разширител

"ИЛИ" верига на модул 2 разширител съвпада с XOR схема.

Таблица 2.5 - истина маса по модул 2 разширител

PI - 1 вход прехвърляне от предходния етап,

PO - 1 прехвърляне изход в MSB.

Въз основа на таблицата на истината пишем системата за собствени функции за всеки изход:

S = A · В · PI + A · В · PI + A · В · PI + A · В · PI

PO = A · В · PI + A · В · PI + A · В · PI + A · В · PI

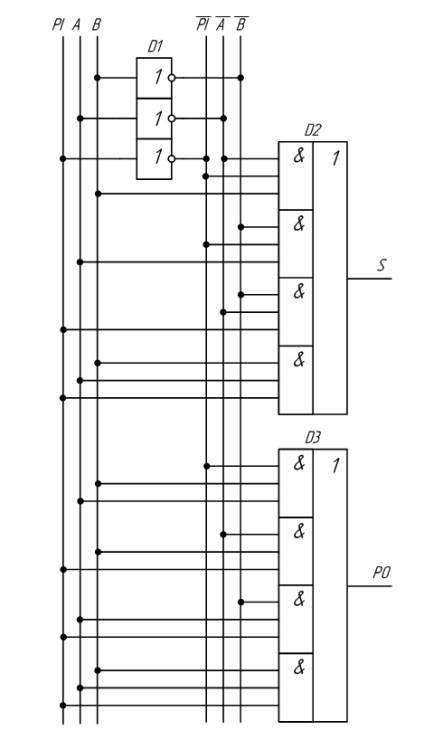

Резултатът е пълен ехидна верига (фигура 2.15).

Фигура 2.16 - По-голяма двоичен един-битов усойница в схеми

3 комплекта за работа

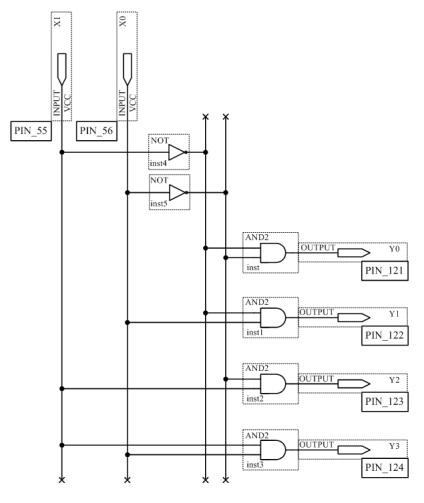

3.1 За да се изследва Принципът на работа на декодера 2 х 4

Конфигуриран FPGA в съответствие с фигура 3.1. Свържете се X0 на входа и X1 S7 и S8 превключватели и Y0 на изхода, У1, У2, Y3 светодиоди LED5, LED6, LED7, LED8. За да направите това, свържете входовете и изходите на декодера към съответните краката на FPGA.

Хранене всички възможни комбинации на логическите нива на входа X0, X1 чрез клавиши S7, S8 и спазване на членки на LED индикатора LED5, LED6, LED7, LED8, попълнете декодер маса истина.

Таблица 3.1 - Таблица декодер

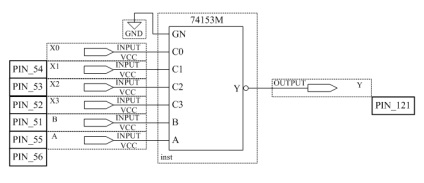

3.4 Действието на 4x1 мултиплексор

Конфигуриран FPGA в съответствие с фигура 3.4.

Таблица 3.5 - Таблица описващ действието на мултиплексор

Брой на комутируем канал

3.5 За да се изследва ехидна верига

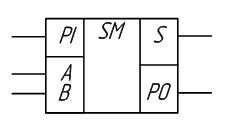

Конфигуриран FPGA в съответствие с фигура 3.5. Тук Pin. Pout съответно прехвърляне на входните и изходните единици, А и В - термините, S - общо.

Фигура 3.5 - Схема разширител

Попълнете таблица ехидна истина (Таблица 3.6).

Таблица 2.7 - Таблица пълен ехидна истина

- Целта на работата.

- проучване проектиране декодер, енкодер, транскодер за дисплея на седем сегмента, мултиплексор, ехидна.

- Истината таблици за всяка верига.

- Заключения относно всяка задача.

5 списък

- Принципът на работа на декодера?

- Как да синтезира декодер с произволна дължина на думата?

- Как енкодер?

- Начертайте таблицата истината на енкодер.

- Как функционира код конвертор за дисплея на седем сегмент?

- Как дисплея на седем сегмент?

- Как мултиплексор?

- Както и в лабораторната работа се извършва проучване на мултиплексор?

- Как лятото?

- Начертайте таблицата истината на енкодер.

- Какво е единица за превод?

Правописна грешка в текста:

Свързани статии