Адер се нарича компютърна единица за аритметични кодове. Adders зависимост от логически схеми се различават от комбинация и се натрупват. Комбинация разширител е комбинаторни верига, която генерира сума на термини, се подава едновременно с входовете на схеми и не съдържа елементи памет. Акумулатори имат памет, в която се натрупват сумиране на резултатите.

По броя на половин разширители входове са разграничени, един единствен и мулти-битови (паралелни) разширители. В зависимост от това как организираната mezhrazryadnye трансфери, разширители са разделени на суматорите с сериен, паралелен и групови смени. В зависимост от системата за брой разширители са ...

бинарни, десетична и други.

В основата на всички суматора представляват един-битов усойница. Освен това, добавянето на п-битови числа се извършва чрез п на един-битов разширители комутиране прехвърлянето им.

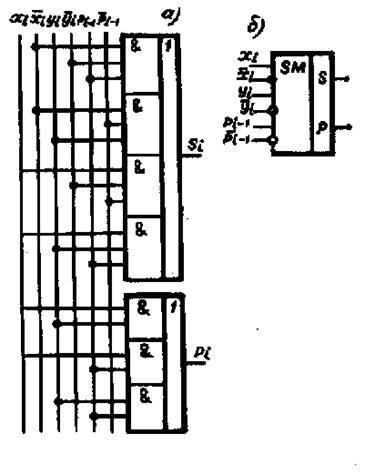

Single-битови разширители. Един-малко разширител предназначен за добавяне на два бита на сходни условия (XI и Yi), с прехвърлянето от предходния етап (Pi-1) и произвежда в една и съща стойност машина цикъл на сумата (Si) и се прехвърля в следващата цифра (Pi). С други думи, едно малко ехидна добавя три бита XI. ай и Пи-1 и Pi и Si форми.

Adders, в която в допълнение на два компонента (х и у) не са взети предвид прехвърлянето на най-маловажния бит, наречен половин разширител. Половин ехидна има два входа (ХI и Yi) и два изхода Pi и Si. маса половин ехидна истина може да бъде написана в таблицата форма. 4.1. в което се вписват на логически функции Si и Pi:

Таблица. 4.1. Таблица. 4.2.

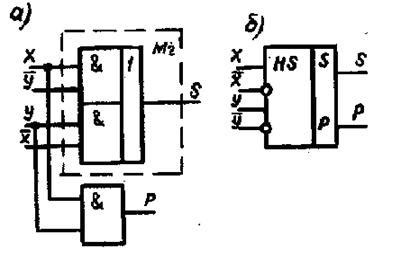

Фиг. 4.9 показва половин разширител верига и наименование на функционалните вериги.

Фиг. 4.9. Схемата на половин ехидна

Един-битова маса ехидна истина е показано в таблица 4.1.

Движеща сила на един-битов пълен ехидна е показано на фиг. 4.10.

Фиг. 4.10. А един-битов пълен ехидна

В зависимост от начина на обработените числата п-битови (обобщено) ниво, суматорите отличават многобитови серийни и паралелни стъпки.

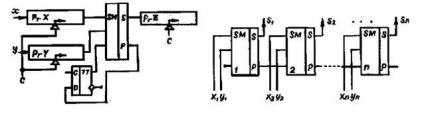

Обработката на последователни Adders отношение побитовото се извършва последователно. Когато това ниво размер, обозначен в сумата на регистър и трансфер се съхранява в един часовник цикъл в по-нататъшно спусъка. Трансфер се подава към суматора заедно с входните условията на последващо изтичане. Процесът продължава, докато резултатът не е напълно оформени. Структурата на мулти-битови етапите на разширител последователни показани на Фиг. 4.11. Shift регистрира PRX надзъртам и се използват за съхранение на операнди и измества надясно. PRZ - получаване на сумата от бита изход от една-битов ехидна на. Побитовото сумиране се извършва в ехидна. Прехвърляне на предходния етап се съхранява в D-тригер.

мулти-битови Adders паралелни бита за действие, се обработват в паралелни условия. Броят на разширители в тях съответства на номера на малко обработени. Чрез прилагане Adders транспортни вериги паралелно действие може да има следната организация: разширители последователно, едновременно и група трансфер.

Трансферът на разширители сериен трансфер разпространява последователно (фигура 4.11) Максимално време за извършване размножаване е:. тåмакс = t1 п, където t1 - време, да размножаване в един разряд; N - броя на битовете на суматора.

Паралелно действие разширители (фиг. 4.12) с едновременно прехвърляне на пренос сигнал се генерира едновременно във всички битове. Обмислете едновременни синтез вериги за носене на 4-битови разширители.

Фиг. 4.11. Сериен разширител Фиг. 4.12. Паралелно ехидна

Паралелни преводи разширители група, където трансфери в рамките на група са оформени едновременно и последователно между групи, наречени разширители с преводи верига.

Свързани статии