Особеността на аритметични устройства е, че двоични сигнали, с двама известни състояния на високи и ниски нива се дължат не само логично, но също така и аритметични стойности 0 и 1, както и операции по тях се подчиняват на законите на аритметиката.

За да кандидатствате двоичните числа изчислително устройство операционна аритметични: събиране, изваждане, умножение, деление, степенуване, логаритмуване и т.н. Чрез аритметика също са специални устройства:

за определяне на четността (паритет)

за сравняване на две множествен битови числа (за сравнение)

за мажоритарен контрол (кворум - елементи)

Всички аритметични операции на двоични числа са намалени до допълнение: изваждане - е добавянето на две числа, едната от които е представен в допълнение до две или на заден ход; умножение - е многократно добавяне и смяна; разделение - е повтаряща се извадят и смяна. Експоненциален, логаритмични и други сложни функции в цифрова електроника, компютърна изчисляват приблизителните формули, включително събиране и умножение.

Адер. ЛЯТНА суматор

Adder на два хомогенни условия се нарича половин разширител и означават HS - ПОЛОВИН SUM - половината от размера.

`

P = AB трансфер (преливник) понякога означен с С, или да CR - прехвърляне.

За да се избегне объркване в означението на логически и аритметични операции в описанието ще бъдат да бъдат определени само от + аритметично аритметични единици, и да подпише V - логика функция или, логично допълнение. марка

При добавяне на две многобитови двоични числа, но два мандата в разширители входове всеки битови да бъде вход за повече прехвърляне на LSB. Само половин ехидна има два входа и по този начин е подходящ за сумиране само най-маловажният бит от гледна точка, и не е подходящ за обобщаване на всички останали битове на условията.

За добавяне на каквито и да било разрядни два компонента, като взема предвид прехвърлянето на най-маловажният бит е един-битов пълен ехидна или просто ехидна.

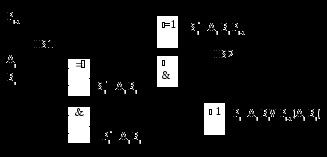

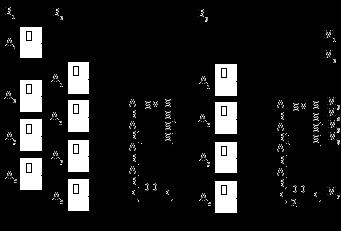

На суматора може да се конструира от два полу-разширител. Първата половина на суматора добавя двата термина HS1 и генерира междинен сума Si "и се прехвърля Pi. Втората половина-разширител добавя HS2 пренос от предходната отговорност Pi-1, с междинно съединение сумата Si-1. резултатът е общата сума на Si. Прехвърляне получи участието на две ХС и допълнителни или портата.

Булеви изрази за Si и Pi след минимизиране и като се вземат предвид всяка друга ще бъде:

Шофиране SM сведени до минимум, тези изрази в NAND порта, нито се използва като основа на чиповете 155 MI 1,2,3. Има изходи

А един-битов усойница може да се използва за добавяне на многоцифрени двоични числа, ако те са представени от сериен код, в който по-ниски цифри следват пред старейшините. В този случай предаването на сигнал от изхода подава към входа на прехвърлянето на същата ехидна чрез забавяне верига, която осигурява съхранение на времето за предаване на един импулс повторение входните цифрови условия. Това е най-бавния метод за добавяне на многоцифрени числа, но това е най-икономичен на оборудването.

Паралелно Освен със сериен трансфер.

Тук, броят на пепелянки е равен на броя на електричество. скорост на пренос Забавяне е ограничен, тъй като сигналът формация обобщава Sn и Pn MSB прехвърляне не може да се случи, докато LSB пренасяне на сигнала не се разпространява по веригата на серия.

Паралелно допълнение с паралелно превод.

прехвърлянето забавяне на време може да бъде намалено чрез въвеждане успоредно преводи, за които се използва ускорен верига трансфер (PAF). В тези схеми, прехвърлянето на всеки бит се получава независимо от съседния транспорт LSB, тя се формира от компонентите на освобождаване и прехвърлят на входния суматора (предишен освобождаване, тя се подава към LSB извършва вход).

За да се опише действието на суматора с паралелно превода да се въведе два допълнителни функции у и П:

γ - генериране на функция за трансфер (преносимо GENERATORION - CRG) γi = Ai Bi; γi = 1 Ако в това аз разряд разширител, който генерира трансфер ако Ai = Bi = 1 и γi = 0 във всички останали случаи.

π - функция прозрачност Разпределение ил (преносимо Разпространяването - CRPP), π = AiVBi, понякога prinimayutπ = Ai

Процесът на формиране на ускорено прехвърлянето описан от уравнението

На практика, γ и π функция е междинните сигнални битове на разширител верига, който сигнал се използва за образуване на паралелно прехвърлянето на всички суматора.

изваждане Техниката дискретни устройства обикновено заменя с добавяне на умаляемото с умалителят когато последният е представена в допълнение до две.

Да предположим, че е необходимо да се получи разлика на две числа A-B, където А и Б - hfphzlyst двоични числа.

B + = B + Bdop

п бита N + 1 бит

В = 1000 ... 0 ... 111 -Bdop = 1 + 1

п бита N + 1 бит

А-В = А-1 + ... 1000

Това означава, че за да се изважда две числа са достатъчни, за да ги добавите, ако това умалител представени в допълнителен код.

С това изваждане, ако разликата е положителна, т.е. A> B, тогава тази разлика ще бъде представен в директен кода и при изпълнението по-стари възрастни, т.е. в 1razryade образува п + 1, което може да се пренебрегне.

Ако такова изваждане на разликата е отрицателно, т.е. А Умножение и деление на двоични числа. Тъй като частичен продукт в цифри от 1 е равен на този брой, и размножаването от 0 дава нули във всички битове, операцията умножение се редуцира до изместване операции и добавяне на частични продукти.

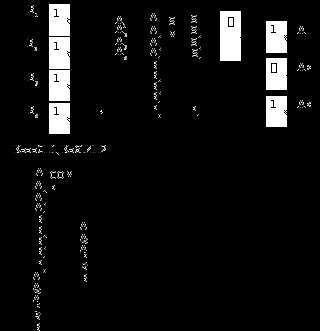

Схема множител chetyrohrazryadnogo брой A4A3A2A1 на трицифрено число B3B2B1, реализирана на чипове тип K155IM3. M7M6M5M4M3M2M1 седем-битов продукт продукция на множителя е оформен чрез умножаване на множителя паралелно към всяка цифра на множителя B 2i логически елементи и добавяне на междинни парчета с промяна от един бит - разширители SM DD1 и DD2.

Прилагане на и порти за извършване на аритметична операция за размножаване в този случай е допустимо, тъй като от една цифра и аритметиката и логично умножение (и функция, заедно) са предмет на общите правила.

Двоичното разделянето на следните операции: изваждане на делителя от дивидент, делител на срязване от една цифра, от получения остатък с разделител, ако остатъкът е по-малък от делителя, делител изместване за друга категория, отново сравнение делител Остатъкът, ако остатъкът през делител, то делител се изважда, а след това отново следва сплитер смяна, отново се сравняват, така че, докато след преминаването му разделител LSB, равна на най-маловажният бит на дивидента. В тези битове, където остатък сравнение разделител показаха, че остатъкът е по-малко от делителя, резултатът в този малко разделение - лично - писмено до нула, останалите битове - 1. Така, разделението се свежда до изваждане, изместване и сравнение.

А със сравнителен продукт (сравнение верига) COMPARU - за сравнение, съпоставя.

Сравнява два мулти-битови числа А и В в мащаб. Обикновено има три изхода. А

Ако ние си спомняме, раздел изваждане на двоични числа, става ясно защо прехвърлянето на сигнал, получен чрез сигнал A> B и A

Почти всеки канал за данни, или всяка памет, ако те не оказват силен метод за контрол, защитен контрол на четността, равенство (паритет - линия) на п вход елемент

Това дава възможност за премахване на невалидните данни, да изисква препредаване и т.н.

Схеми за контрол на паритетен бит освен п M2 елемент, който изпълнява пирамида входни елементи 2 = 1 (без OR) (между другото, за два входа М2 = 1 еквивалент), допълва контролни вериги изберете функция: от странност или гладкост.

Възли за контрол на мнозинството.

Те са прости в смисъл вериги, което позволява не само се идентифицират, но също така и да се коригират грешки, които се случват по време на предаването и обработка на данни. Той използва три канала - при предаване, или три блока - за обработка на данни; изходни данни, предоставени им мнозинство блок за управление (мажоризация възел кворум елемент), който генерира от тях един-единствен изходен сигнал на базата на гласуване "две от три", продукцията е логиката 1, ако две или три изхода влезте 1. В възелът обикновено се прилага контрол мнозинство елемент, което позволява да се определи броя на Неуспешно (несходни с останалата част) или канал блок. AER - АДРЕСС грешка. MSB - НАЙ SIGNIFICAT БТТ - най-важната част. LSB - ни най-малко - най-ниската цифра на двоичен код се посочва номера на неуспешната канал.

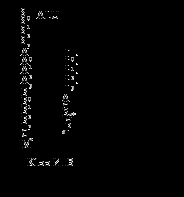

Аритметика-логическо устройство ALU-аритметика и Логика UNIT

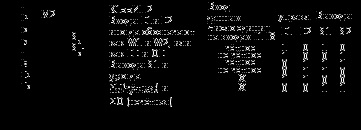

Технологията на микропроцесора са основни елементи на ALU. За М = Н (високо) чип изпълнява логически функции на четири цифри входни променливи А и Б. Изборът на определена функция на 16 възможно даден набор от вход контролни сигнали SO ... S3:

Когато М = L (ниско) IP3 ALU извършва аритметични операции върху четири цифри двоични числа А и Б. Комплектът (комбинация) на входния сигнал SO ... S3 определя един от 16 възможни операции:

Има Asdv равно на А, като всеки бит, който е изместен в посока на по-висок ранг.

Cn - вход и Cntu - извършване изход

G и F - у функции генерират изходи трансфер и π - прехвърляне на прозрачност за верига връзка на ускореното транспорт K155 ИП4.

Свързани статии